FPGA LVDS CSI2

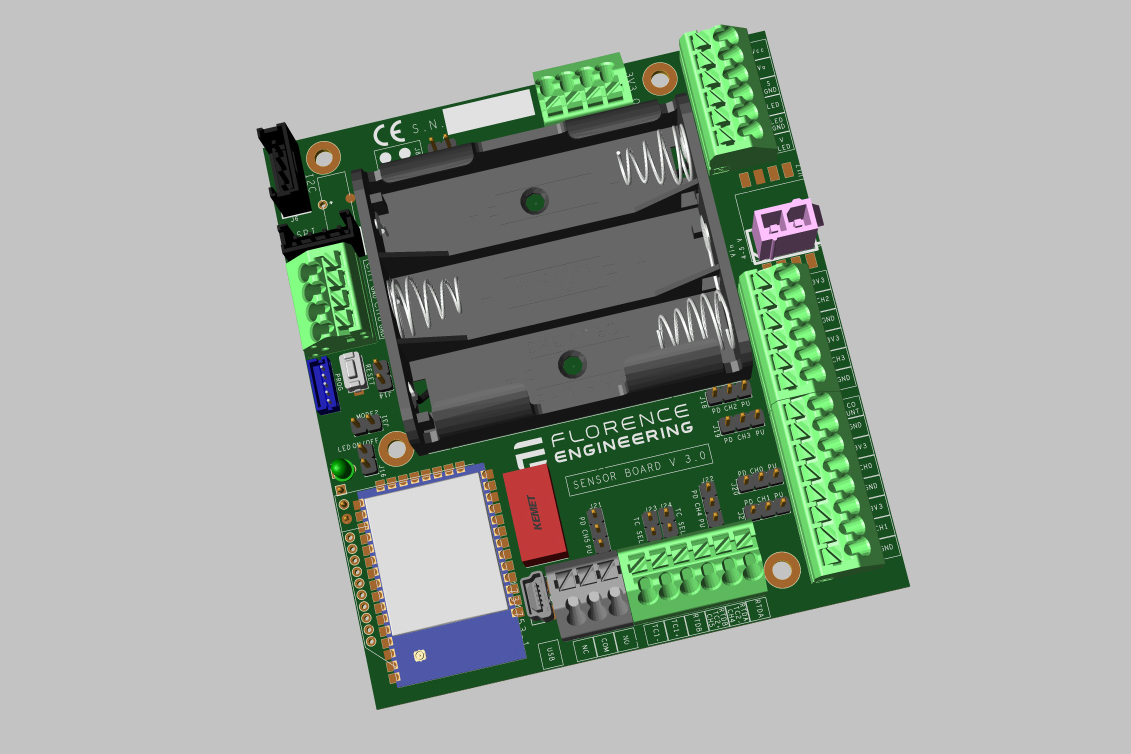

Florence Engineering developed an FPGA-based protocol converter for a strategic customer in the industrial automation sector. The device was designed to convert an input LVDS stream to an output CSI-2 bus.

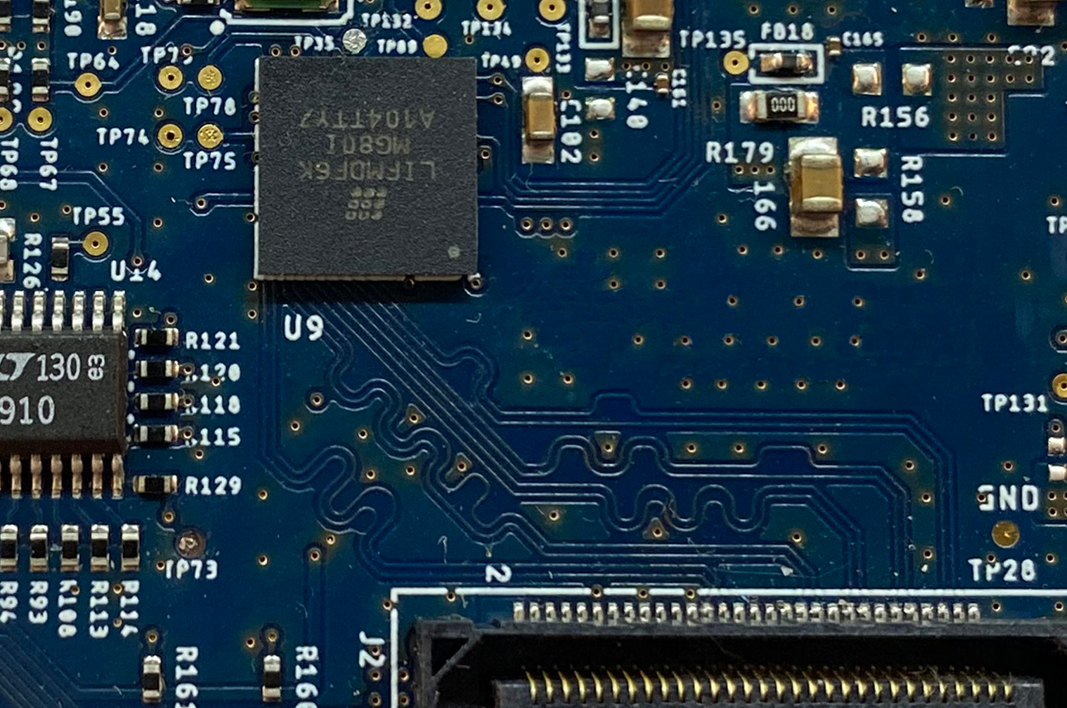

The converter, implemented in verilog on a Lattice® FPGA, is capable of handling data up to 600 Mbps per lane, with 4 input data lanes and 4 output data lanes. The device accepts incoming LVDS RAW data, and performs packaging and encapsulation in the payload of a “long packet” in the CSI-2 protocol. Furthermore, the converter manages all phases of communication.

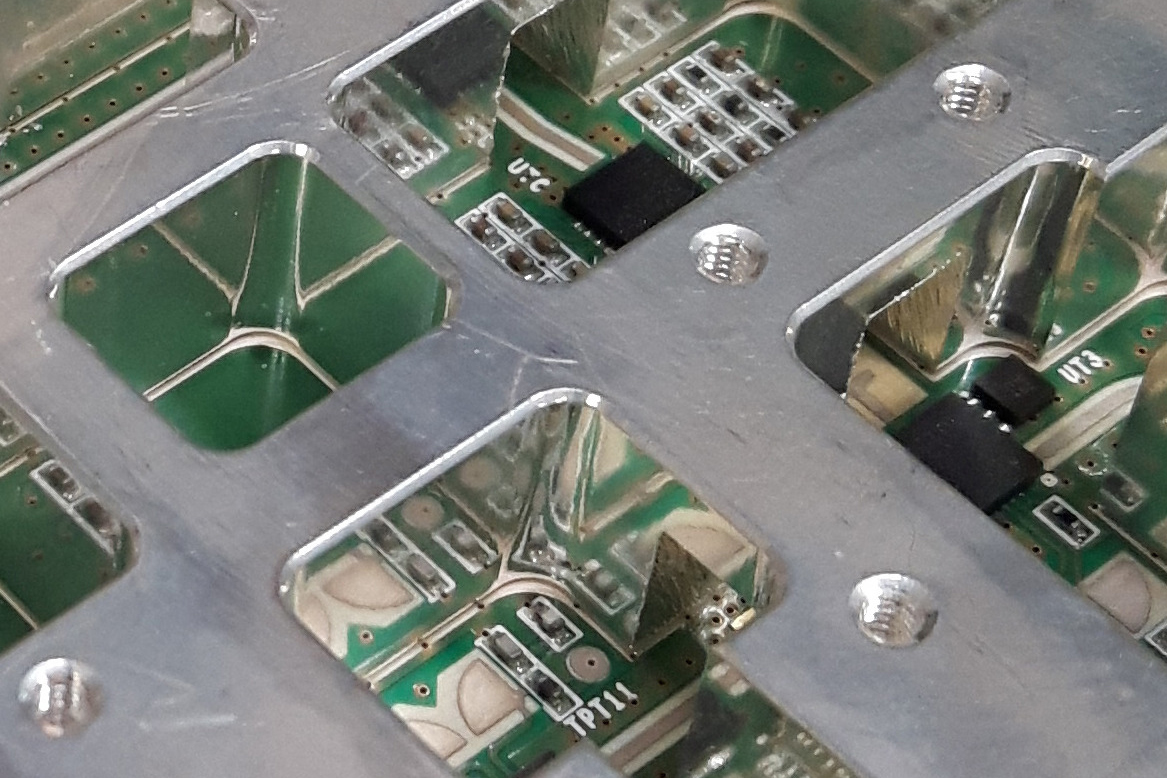

This converter was necessary to bridge the gap between sensors with direct outputs of sampled data and advanced processors with standard interfaces and protocol communications. Thanks to the converter, sensor data can be easily integrated with existing processors, thus simplifying communication between devices and improving the efficiency of the system as a whole.