FPGA LVDS CSI2

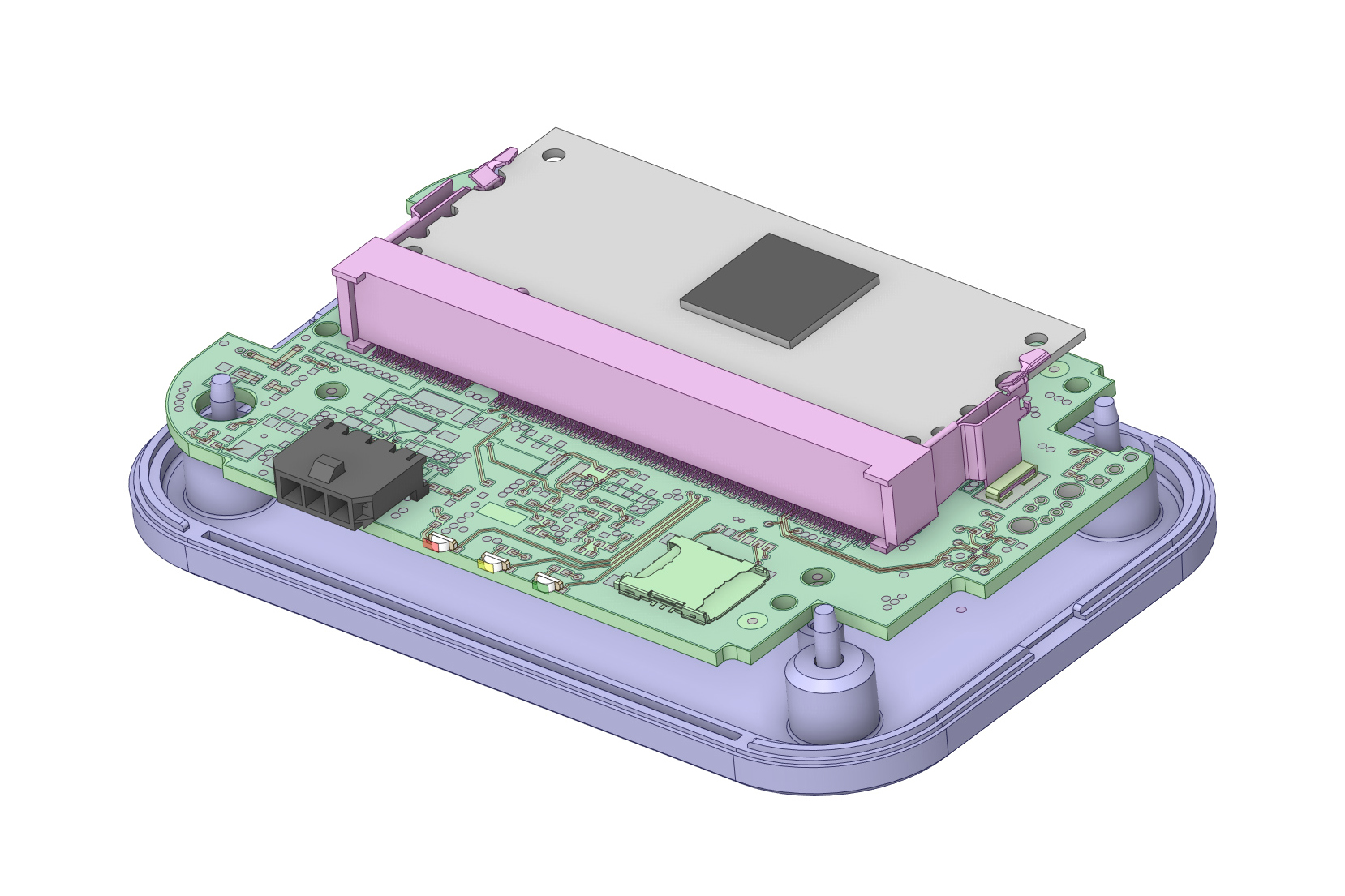

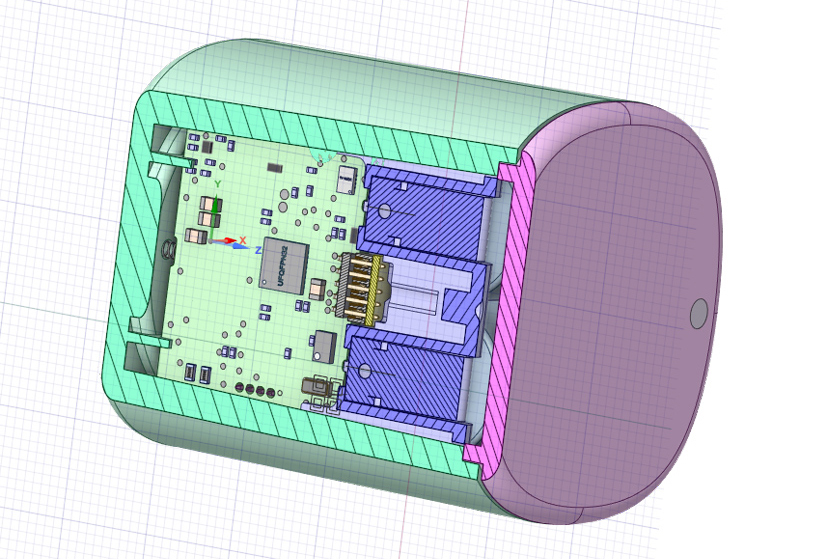

Florence Engineering ha sviluppato un convertitore di protocollo basato su FPGA per un cliente strategico nell’ambito dell’industrial automation. Il dispositivo è stato progettato per convertire uno stream LVDS in ingresso in un bus CSI-2 in uscita.

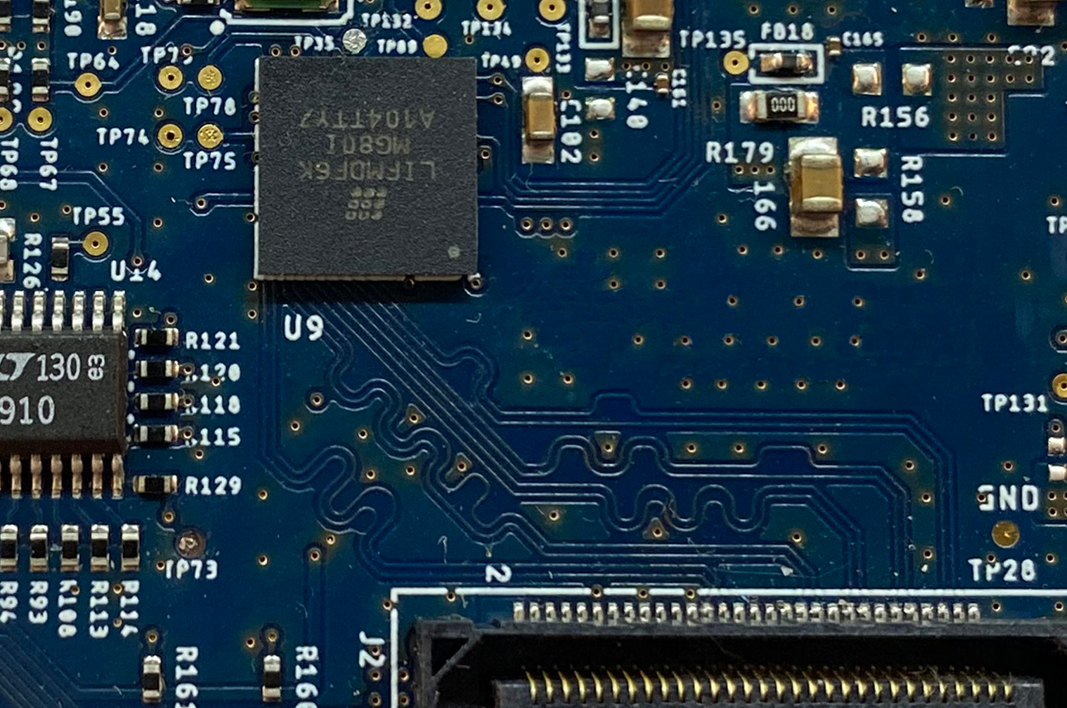

Il convertitore, implementato in verilog su un FPGA Lattice®, è in grado di gestire dati fino a 600 Mbps per lane, con 4 lane dati in ingresso e 4 lane dati in uscita. Il dispositivo accetta dati LVDS in ingresso di tipo RAW, li impacchetta e li incapsula all’interno del payload di un “long packet” nel protocollo CSI-2. Inoltre, il convertitore gestisce tutte le fasi della comunicazione.

Questo convertitore si è reso necessario per colmare il divario tra i sensori con uscite dirette dei dati campionati e i processori evoluti con interfacce standard e comunicazioni a protocollo. Grazie al convertitore, i dati dei sensori possono essere facilmente integrati con i processori esistenti, semplificando così la comunicazione tra i dispositivi e migliorando l’efficienza del sistema nel suo complesso.

altri lavori